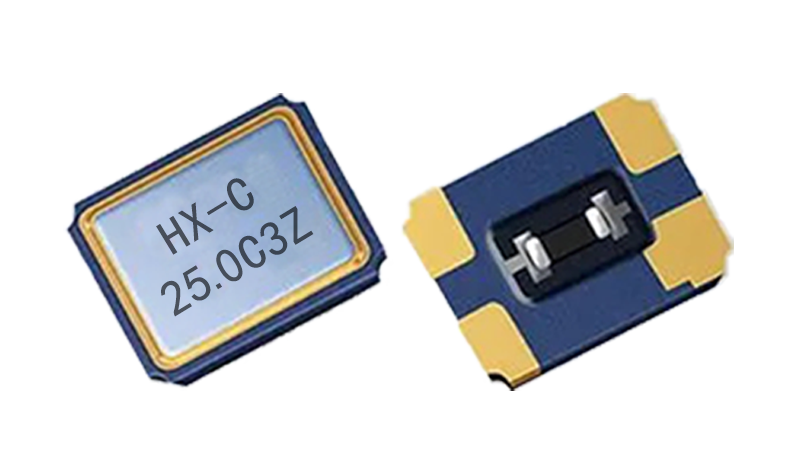

内蒙古4M晶振 深圳市华昕电子供应

- ¥0.000

- 更新 2024-10-15

- 地区 广东深圳市深圳市福田区振中路新亚洲国利大厦1425

- 联系 古尚宇 13682691851

- 深圳市华昕电子有限公司进入店铺 >>

信息介绍 / Information introduction

使用晶振实现精确的时间延迟,主要依赖于晶振产生的稳定时钟信号。以下是一些基本步骤:选择适当的晶振:首先,根据所需的延迟精度和稳定性,选择具有合适频率和性能的晶振。晶振的频率越高,能实现的延迟精度也越高。设计计数电路:利用晶振产生的时钟信号,设计一个计数电路。当需要实现特定的时间延迟时,可以预设一个计数器值,并在时钟信号的驱动下进行计数。当计数器达到预设值时,即表示时间延迟已完成。校准和测试:由于实际电路中的元器件参数和环境因素可能对时间延迟产生影响,因此需要对电路进行校准和测试。通过调整计数器的预设值或引入补偿电路,确保实际的时间延迟与预设值一致。集成到系统中:将实现时间延迟的电路集成到整个系统中,并根据需要进行调试和优化。确保时间延迟电路与其他电路模块的协同工作,以实现整体系统的稳定运行。需要注意的是,由于晶振的频率稳定性和温度特性等因素,实现的时间延迟可能存在一定的误差。因此,在实际应用中,需要根据具体需求和环境条件进行适当的调整和优化。晶振的分类及其主要参数。内蒙古4M晶振

晶振的Q值,也称为“品质因数”,是晶振的一个重要电气参数。它表示了周期存储能量与周期损失能量的比值。在石英晶体谐振器中,Q值越大,其频率的稳定度就越高。具体来说,Q值的大小反映了晶振内阻的大小、损耗的大小、需要的激励功率的大小以及起振的难易程度。Q值大,说明晶振内阻小、损耗小、需要的激励功率小、容易起振,晶振稳定性越好。Q值对电路性能的影响主要体现在以下几个方面:频率稳定性:Q值越高,晶振的频率稳定性越好。这是因为Q值大意味着晶振的损耗小,能够更好地维持其振荡频率。起振性能:Q值大的晶振更容易起振。在电路设计中,如果晶振的起振困难,可能会导致电路无法正常工作。因此,选择Q值大的晶振有助于提高电路的起振性能。抗干扰能力:Q值大的晶振具有较好的抗干扰能力。在复杂的电磁环境中,晶振容易受到外界干扰而导致性能下降。Q值大的晶振能够更好地抵御外界干扰,保持其稳定性和准确性。总之,晶振的Q值是衡量其性能的重要指标之一。在电路设计中,选择Q值合适的晶振有助于提高电路的频率稳定性、起振性能和抗干扰能力。进口晶振选型指南如何对晶振进行保护以避免损坏?

晶振在电路中的主要作用是提供稳定的时钟信号。时钟信号是电子设备中至关重要的信号之一,它用于同步各个电路模块的工作,确保它们能够按照正确的时间序列进行操作。晶振,作为由晶体材料制成的振荡器,能够以非常稳定的频率振荡。这种稳定性使得晶振成为电子设备中理想的时钟信号源。在电路中,晶振通常被连接到时钟线路上,通过振荡产生一个稳定的方波信号,这个信号即作为时钟信号供电路中的其他部分使用。除了提供稳定的时钟信号外,晶振还具有多个重要特点。首先,它具有高频率精度,其频率偏差可以达到几十或几百万分之一,这确保了时钟信号的准确性。其次,晶振的相位噪声较低,从而能够提供优异的信号质量。再者,晶振展现出高稳定性,无论是在温度变化还是在长期运行过程中,都能保持稳定的振荡频率。晶振不仅影响着电路的时钟信号精度和稳定性,还关系到电路的整体性能和可靠性。在数字电路中,晶振的作用尤为突出,它提供了一个时序控制的标准时刻,确保系统各部分能够有序、同步地工作。晶振的起振时间短暂,为几毫秒,这对于需要快速启动和实时响应的应用至关重要。尽管晶振在工作时会产生一定的噪声,但噪声水平通常很低,不会对大多数应用造成明显影响。

晶振的驱动电平和功耗是晶振性能的两个重要参数,但它们的具体数值会因晶振的型号、规格和应用场景的不同而有所差异。驱动电平是指为晶振提供正常工作所需的电压或电流水平。合适的驱动电平可以确保晶振的稳定性和频率精度。驱动电平过高可能会导致晶振过热或损坏,而驱动电平过低则可能使晶振无法正常工作。因此,在选择和使用晶振时,需要根据具体的规格和应用需求来确定合适的驱动电平。功耗则是指晶振在工作过程中消耗的电能。晶振的功耗主要包括静态功耗和动态功耗两部分。静态功耗是晶振在静止状态下消耗的电能,主要由晶体的固有损耗和电路中的静态电流引起。动态功耗则是晶振在振荡过程中消耗的电能,与晶振的振荡频率和电路中的动态电流有关。一般来说,晶振的功耗较低,以毫瓦(mW)为单位。但在一些低功耗的应用场景中,如移动设备、物联网设备等,对晶振的功耗要求会更加严格。需要注意的是,晶振的驱动电平和功耗并不是固定不变的,它们会受到环境温度、电源电压和负载电容等因素的影响而发生变化。因此,在实际应用中,需要根据具体的应用场景和条件来选择合适的晶振,并进行相应的测试和校准。选择晶振时需要考虑的五个关键点。

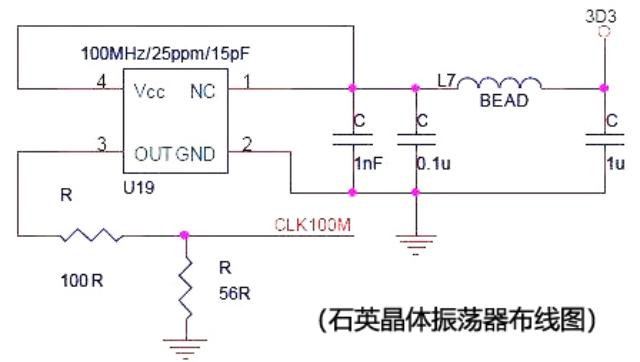

晶振的并联电阻和串联电阻在电路中起着不同的作用,对电路有不同的影响。首先,并联电阻(也被称为反馈电阻)的主要作用是使反相器在振荡初始时处于线性工作区。这有助于稳定无源晶振的输出波形。例如,MHz晶振建议并联1M欧姆的电阻,而KHz晶振则建议并联10M欧姆的电阻。此外,并联电阻还可以提高晶振的抗干扰能力,防止晶振受到外界电磁干扰。其次,串联电阻则主要用于预防晶振被过分驱动。当无源晶振输出波形出现削峰或畸变时,可能意味着晶振存在过驱现象。此时,增加串联电阻可以限制振荡幅度,防止反向器输出对晶振过驱动而将其损坏。串联电阻与匹配电容组成网络,可以提供180度相移,同时起到限流的作用。串联电阻的阻值一般在几十欧姆,具体阻值应根据晶振本身电阻及过驱程度来确定。一般来说,串联电阻的值越小,振荡器启动得越快。总的来说,晶振的并联电阻和串联电阻在电路中各自发挥着关键的作用,通过调整这些电阻的阻值,可以优化晶振的性能,确保电路的稳定性和可靠性。晶振的谐振频率是如何确定的?进口晶振选型指南

晶振的制造过程是怎样的?内蒙古4M晶振

晶振的精度对电路的时序有着直接且明显的影响。晶振作为电路中的时钟源,为电路中的各个部分提供基准频率,确保它们能够按照正确的时序进行工作。首先,晶振的精度决定了电路中的时钟信号的准确度。时钟信号是电路时序控制的基础,它决定了电路中各个部分的工作节奏。如果晶振的精度不高,时钟信号就会产生偏差,导致电路中的时序控制出现误差。这种误差可能表现为数据传输的延迟、信号处理的错乱等问题,严重影响电路的性能和稳定性。其次,晶振的精度还会影响电路的时序裕量。时序裕量是指电路在时序控制上允许的比较大偏差范围。如果晶振的精度较低,那么电路的时序裕量就会减小,电路对时序误差的容忍度就会降低。这可能导致电路在受到一些微小的干扰或变化时,就无法正常工作,降低了电路的可靠性和稳定性。因此,在选择晶振时,需要根据电路的时序要求来选择合适的晶振精度。对于需要高精度时序控制的电路,如高速通信、实时控制等应用,应选择高精度的晶振来确保电路的稳定性和可靠性。内蒙古4M晶振

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。