南宁低相位噪声差分晶振 深圳市华昕电子供应

- ¥0.000

- 更新 2024-09-20

- 地区 广东深圳市深圳市福田区振中路新亚洲国利大厦1425

- 联系 古尚宇 13682691851

- 深圳市华昕电子有限公司进入店铺 >>

信息介绍 / Information introduction

差分晶振的电压控制功能对于设备的频率稳定性、精度以及性能优化起到了关键作用。差分晶振,作为一种特殊的振荡器,其特点在于采用了差分电路结构,使得其输出信号具有更好的稳定性和抗干扰能力。差分晶振的电压控制功能主要体现在其能够通过外部电压的调整来精确地控制其输出频率。这种功能在通信、导航、计算机等领域有着广泛的应用。例如,在无线通信系统中,差分晶振的电压控制功能可以确保信号的准确传输,避免因频率偏差导致的通信错误。差分晶振的电压控制原理主要基于压控振荡器(VCO)的设计。通过调整输入到差分晶振的电压,可以改变其内部的电场分布,从而实现对输出频率的精确控制。这种控制方式具有响应速度快、调节范围宽、稳定性高等优点。然而,差分晶振的电压控制功能也面临一些挑战。首先,电压的波动和噪声可能会对晶振的性能产生干扰,因此需要采取有效的滤波和稳定措施。其次,随着温度的变化,晶振的性能也会发生变化,因此需要对温度进行补偿以确保稳定的输出频率。总的来说,差分晶振的电压控制功能为现代电子设备提供了重要的性能保障。通过优化设计和采用先进的控制算法,可以进一步提高差分晶振的性能和稳定性,满足各种复杂应用场景的需求。差分晶振与普通晶振有何区别?南宁低相位噪声差分晶振

差分晶振的启动时间分析差分晶振,其启动时间对于设备的整体性能有着重要影响。那么,差分晶振的启动时间究竟需要多久呢?

首先,我们要明确晶振的启动时间是指从刚刚接上电源开始,到晶振可正常工作所需要的时间。这个时间的长短取决于多种因素。电容的充电时间是影响晶振起振时间的一个重要因素。在晶振电路中,外部电容的充电时间越长,晶振起振时间也就越长。因此,优化电容的选择和电路设计,可以有效缩短晶振的启动时间。此外,晶振管自身的参数,如内部电容、电感、阻抗等,也会对启动时间产生影响。这些参数的优化,同样有助于缩短启动时间。外部环境中的干扰也是影响晶振启动时间不可忽视的因素。例如,电源电压的波动、环境温度的变化以及电磁信号的干扰等都可能延长晶振的启动时间。因此,在实际应用中,需要尽量减小这些外部干扰,以保证晶振的稳定性和快速启动。值得注意的是,虽然差分晶振的启动时间通常较短,但在某些特殊情况下,如高温环境或电源电压不稳定的情况下,启动时间可能会变得更长。因此,在这些特殊环境下,需要特别关注晶振的启动性能。综上所述,差分晶振的启动时间受多种因素影响,包括电容的充电时间、晶振管自身参数以及外部环境干扰等。 南宁低相位噪声差分晶振差分晶振的自动相位控制(APC)功能如何?

当电压施加在晶体上时,晶体将以固定的频率振荡。差分晶振通过利用两个晶体振荡器,并将它们的振荡信号分成两个相位相反的输出信号,从而实现差分输出。

差分晶振的基本构成部分是一对振荡石英晶体,中间夹有放大器和相位移器。这两个晶振之间的输出信号相位差为180度,通过叠加使输出频率为两个晶振频率的差值。这种相位差的设计使得差分晶振具有更高的抗噪性,因为两个相位相反的信号对于共模噪声的抑制能力更强。

差分晶振的工作过程可以简单描述为:当电压施加在晶体上时,晶体开始振荡,产生一定频率的信号。这个信号被分成两个相位相反的部分,然后通过差分放大器进行放大和处理。差分放大器将这两个相位相反的信号进行叠加,产生稳定的差分输出信号。这个差分输出信号可以通过引脚连接到其他电路,如通信接口、滤波器、功率放大器等。

差分晶振的优点在于其能够提供更为稳定的时钟信号,并且具有更高的抗噪性。这使得差分晶振在需要较高稳定度和抗噪声能力的特定应用场合中,如高速USB、PCIe等高速通信总线,具有多样的应用前景。

差分晶振的工作原理是通过利用两个晶体振荡器产生相位相反的输出信号,并通过差分放大器进行放大和处理,从而得到稳定的差分输出信号。

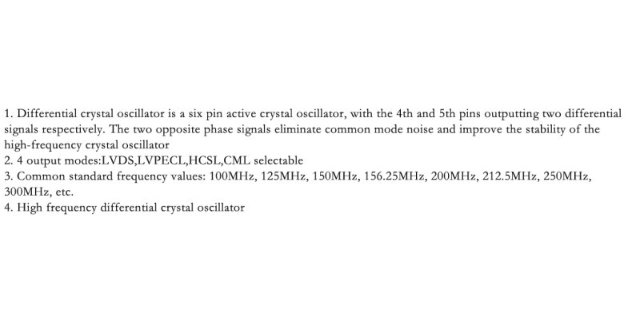

差分晶振的LVDS、LVPECL、HCSL、CML模式介绍及其相互转换

差分晶振LVDS、LVPECL、HCSL和CML是常见的输出模式,每种模式都有其独特的特点和应用场景。LVDS,即低压差分信号,通过两个互补的信号线传输数据,提高抗干扰能力和传输距离,适用于高速数据传输和显示接口。而LVPECL则采用差分对放大器驱动射极跟随器,输出直流电流,常用于需要精确和稳定时钟信号的应用。HCSL,即高速电流转向逻辑,是一种低电压、低功耗的差分信号,通过控制电流方向传输数据,常用于系统内部的高速串行通信。CML,即电流模式逻辑,使用差分共发射极晶体管和集电极电阻,实现信号的摆幅,适用于需要快速响应和稳定性能的应用。在实际应用中,差分逻辑电平之间的转换是必不可少的。这通常通过在驱动器侧和接收器侧之间增加衰减电阻和偏置电路来实现,从而将一个差分逻辑转换为其他类型的差分逻辑,以满足不同系统的需求。差分逻辑电平匹配原则包括确保驱动器件的输出电压在负载器件的输入电压范围内,并保持一定的噪声容限,同时驱动器件还需满足负载器件对电流的需求。综上所述,差分晶振的LVDS、LVPECL、HCSL和CML模式各具特色,相互转换则是实现系统间互操作的关键。 差分晶振与数字电路之间的接口设计需要注意哪些问题?

差分晶振的寿命:因素与影响差分晶振,作为电子设备中的关键组件,其性能和使用寿命对于整个系统的稳定性和可靠性具有至关重要的作用。然而,关于差分晶振的寿命问题,实际上并没有一个固定的答案,因为它受到多种因素的影响。首先,晶振的制造工艺对其寿命有着直接的影响。石英晶体的切割、镀膜、电极制作、封装以及后续的调试与测试,每一步都需要精确的操作和严格的质量控制。任何环节的失误都可能导致晶振的性能下降,从而影响其使用寿命。其次,差分晶振的工作环境也是决定其寿命的重要因素。温度是一个关键的环境因素,特别是对于工业级应用的晶振,如YSO230LR,它能在-40℃至+85℃的环境下正常运行。超出这个范围,晶振的性能可能会受到影响,从而缩短其寿命。此外,电压也是一个重要的影响因素。晶振的负载电容与其工作环境中的电压有直接关系。过激或欠激的电压都可能导致晶振的老化,从而影响其使用寿命。总的来说,差分晶振的寿命并不是一个固定的数字,而是受到制造工艺、工作环境、电压等多种因素的影响。为了延长差分晶振的使用寿命,我们需要选择高质量的产品,并确保其在合适的工作环境中运行,同时对其进行定期的维护和检查。差分晶振在高温环境下的性能如何?南宁低相位噪声差分晶振

差分晶振的驱动电路如何设计?南宁低相位噪声差分晶振

差分晶振作为一种高精度、高稳定度的频率源,在现代电子设备中发挥着至关重要的作用。然而,任何晶振都无法完全避免相位抖动的存在,差分晶振也不例外。相位抖动是衡量晶振性能的重要指标之一,它直接关系到输出信号的稳定性和可靠性。

差分晶振的相位抖动主要来源于内部电路噪声、外部环境干扰以及温度变化等因素。内部电路噪声是不可避免的,但可以通过优化电路设计、选用低噪声器件等方式来降低其影响。外部环境干扰,如电磁辐射、机械振动等,也可能对差分晶振的相位稳定性产生负面影响。此外,温度变化也是导致相位抖动的重要因素,因为晶振的频率随温度变化而发生漂移。

为了降低差分晶振的相位抖动,制造商通常会采用一系列技术手段。例如,采用温度补偿技术来减小温度变化对频率稳定性的影响;使用低噪声放大器和滤波器来降低内部电路噪声;以及采用屏蔽和隔离措施来减少外部环境干扰。这些措施能够显著提高差分晶振的相位稳定性,使其在各种应用场合中都能表现出优异的性能。

总的来说,差分晶振的相位抖动是一个复杂的问题,涉及多个方面的因素。尽管无法完全消除相位抖动,但通过优化设计和采用先进技术,可以将其控制在较小的范围内,从而满足大多数应用的需求。 南宁低相位噪声差分晶振

免责声明: 本页面所展现的信息及其他相关推荐信息,均来源于其对应的用户,本网对此不承担任何保证责任。如涉及作品内容、 版权和其他问题,请及时与本网联系,我们将核实后进行删除,本网站对此声明具有最终解释权。